Instructions

# Tektronix

### DAS<sup>®</sup> 9200 Series & TLA 500 Series Certification Procedures

070-9470-98

Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to all safety summaries prior to performing service. Copyright © Tektronix, Inc. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the Commercial Computer Software – Restricted Rights clause at FAR 52.227-19, as applicable.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Printed in the U.S.A.

Tektronix, Inc., P.O. Box 1000, Wilsonville, OR 97070-1000

TEKTRONIX, TEK, and DAS are registered trademarks of Tektronix, Inc.

## **Table of Contents**

| General Safety Summary                                                                                                                                                                                   | v                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Service Safety Summary                                                                                                                                                                                   | ix                                |

| Preface                                                                                                                                                                                                  | xi                                |

| Introduction                                                                                                                                                                                             | 1<br>2<br>3<br>5                  |

| Equipment Required                                                                                                                                                                                       | 5<br>7                            |

| Procedure 1: DAS 9219/9220 Mainframes<br>Time Base Accuracy                                                                                                                                              | 9<br>9                            |

| Procedure 2: DAS 9221 and TLA 510/TLA 520 Mainframes                                                                                                                                                     | 13                                |

| Time Base Accuracy                                                                                                                                                                                       | 13                                |

| Procedure 3: 92E9 Expansion Mainframe                                                                                                                                                                    | <b>17</b><br>17                   |

| Procedure 4: 92A16 Acquisition Board and 92A16E Expansion                                                                                                                                                | •••                               |

| Board                                                                                                                                                                                                    | <b>23</b><br>23<br>25             |

| Procedure 5: 92A96/92C96 Acquisition Board                                                                                                                                                               | 33                                |

| Threshold Accuracy                                                                                                                                                                                       | 33                                |

| Procedure 6: 92HS8 Interface Board and Probe CabinetsCalibrator Accuracy: Probe CabinetTime Base Accuracy: Probe CabinetTime Base Accuracy: Master Interface BoardData Threshold Accuracy: Probe Cabinet | <b>39</b><br>40<br>41<br>43<br>46 |

| Procedure 7: 92S16/92SX109 Pattern Generator Board<br>Pod Clock Maximum Skew<br>Threshold Accuracy                                                                                                       | <b>55</b><br>55<br>59             |

| Procedure 8: 92S32/92SX118 Pattern Generator Board         Pod Clock Maximum Skew                                                                                                                        | <b>63</b><br>63                   |

| Appendix A: 92A96 Acquisition Fixture         Material Required         Build Procedure                                                                                                                  | <b>71</b><br>71<br>71             |

| Appendix B: Threshold Fixture         Material Required         Build Procedure                                                                                                                          | <b>73</b><br>73<br>73             |

## List of Figures

| Figure 1: Certification Procedure Tasks                                                               | 4  |

|-------------------------------------------------------------------------------------------------------|----|

| Figure 2: Controller Board 100 MHz Time Base Clock Test Point<br>Locations (DAS 9219/9220 Mainframes) | 10 |

| Figure 3: Controller Board 100 MHz Time Base Clock Test Point<br>Location (DAS 9221/TLA Mainframes)   | 14 |

| Figure 4: DAS 92E9 Expansion Slave Board Test Point Locations                                         | 19 |

| Figure 5: 92A16 Test Point Locations (back of board)                                                  | 24 |

| Figure 6: Data and Clock Threshold Test Point Locations                                               | 34 |

| Figure 7: 92HS8 Memory Board Test Point Locations<br>(back of board)                                  | 42 |

| Figure 8: 92HS8 Probe Cabinet Data Threshold Accuracy         Equipment Setup                         | 47 |

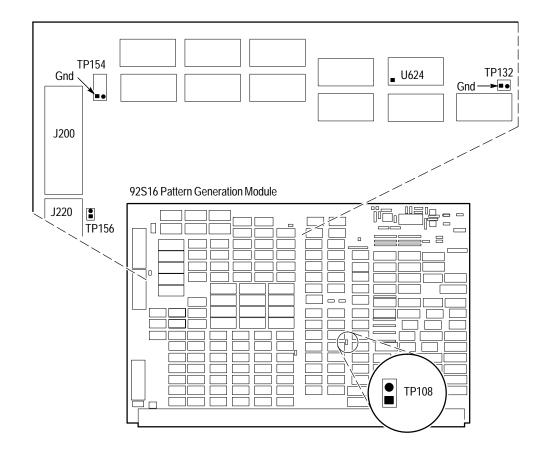

| Figure 9: 92S16 Test Point Locations                                                                  | 57 |

| Figure 10: 92832 Test Point Locations                                                                 | 65 |

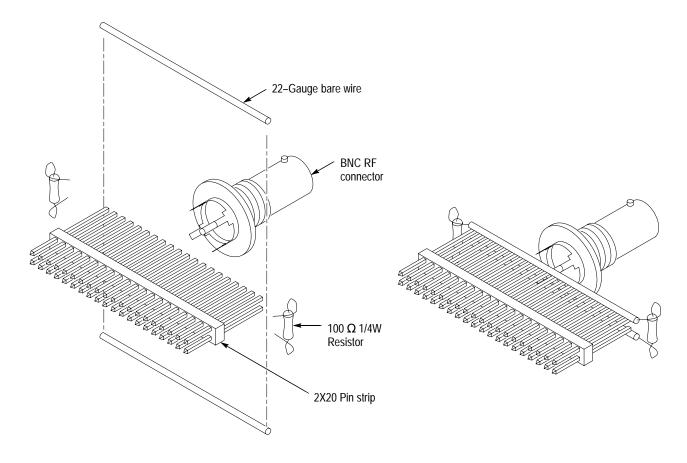

| Figure 11: 92A96 Acquisition Fixture Construction                                                     | 72 |

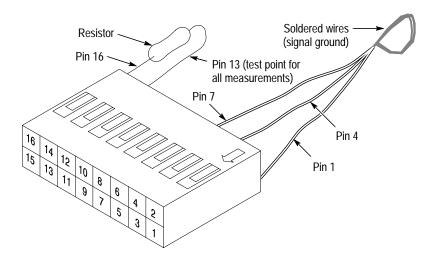

| Figure 12: Threshold Fixture                                                                          | 74 |

### **List of Tables**

| Table 1: Products Certified                                        | 2  |

|--------------------------------------------------------------------|----|

| Table 2: Products Not Certified                                    | 3  |

| Table 3: Required Test Equipment                                   | 6  |

| Table 4: Pod Clock Output Skew (Not Edge Positioned),Steps 6 and 7 | 66 |

| Table 5: Pod Clock Output Skew (Edge Positioned),Steps 14 and 15   | 67 |

| ±                                                                  |    |

Table of Contents

## **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it.

Only qualified personnel should perform service procedures.

#### **Injury Precautions**

| Use Proper Power Cord                        | To avoid fire hazard, use only the power cord specified for this product.                                                                                                                                                                                                                         |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ground the Product                           | This product is grounded through the grounding conductor of the power cord. To<br>avoid electric shock, the grounding conductor must be connected to earth<br>ground. Before making connections to the input or output terminals of the<br>product, ensure that the product is properly grounded. |

| Do Not Operate Without<br>Covers             | To avoid electric shock or fire hazard, do not operate this product with covers or panels removed.                                                                                                                                                                                                |

| Use Proper Fuse                              | To avoid fire hazard, use only the fuse type and rating specified for this product.                                                                                                                                                                                                               |

| Do Not Operate in<br>Wet/Damp Conditions     | To avoid electric shock, do not operate this product in wet or damp conditions.                                                                                                                                                                                                                   |

| Do Not Operate in an<br>Explosive Atmosphere | To avoid injury or fire hazard, do not operate this product in an explosive atmosphere.                                                                                                                                                                                                           |

| Avoid Exposed Circuitry                      | To avoid injury, remove jewelry such as rings, watches, and other metallic objects. Do not touch exposed connections and components when power is present.                                                                                                                                        |

#### **Product Damage Precautions**

**Use Proper Power Source** Do not operate this product from a power source that applies more than the voltage specified.

| Use Proper Voltage<br>Setting             | Before applying power, ensure that the line selector is in the proper position for<br>the power source being used. |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Provide Proper Ventilation                | To prevent product overheating, provide proper ventilation.                                                        |

| Do Not Operate With<br>Suspected Failures | If you suspect there is damage to this product, have it inspected by qualified service personnel.                  |

### Safety Terms and Symbols

**Terms in This Manual** These terms may appear in this manual:

High Voltage

**WARNING**. Warning statements identify conditions or practices that could result in injury or loss of life.

**CAUTION.** Caution statements identify conditions or practices that could result in damage to this product or other property.

| Terms on the Product   | These terms may appear on the product: |                        |                     |                       |        |

|------------------------|----------------------------------------|------------------------|---------------------|-----------------------|--------|

|                        | DANGER indica<br>marking.              | ates an injury hazard  | immediately access  | sible as you read the | •      |

|                        | WARNING indi marking.                  | cates an injury hazaro | l not immediately a | accessible as you rea | ad the |

|                        | CAUTION indic                          | cates a hazard to prop | erty including the  | product.              |        |

| Symbols on the Product | The following sy                       | mbols may appear or    | n the product:      |                       |        |

|                        |                                        |                        | $\triangle$         |                       |        |

|                        | DANGER                                 | Protective Ground      | ATTENTION           | Double                |        |

(Earth) Terminal

Insulated

Refer to Manual

### **Certifications and Compliances**

| CSA Certified Power<br>Cords | CSA Certification includes the products and power cords appropriate for use in<br>the North America power network. All other power cords supplied are approved<br>for the country of use. |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Compliances                  | Consult the product specifications for Overvoltage Category and Safety Class.                                                                                                             |

| Overvoltage Category         | Overvoltage categories are defined as follows:                                                                                                                                            |

|                              | CAT III: Distribution level mains, fixed installation                                                                                                                                     |

|                              | CAT II: Local level mains, appliances, portable equipment                                                                                                                                 |

|                              | CAT I: Signal level, special equipment or parts of equipment, telecommunica-<br>tion, electronics                                                                                         |

# Service Safety Summary

|                                          | Only qualified personnel should perform service procedures. Read this <i>Service Safety Summary</i> and the <i>General Safety Summary</i> before performing any service procedures.                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Do Not Service Alone                     | Do not perform internal service or adjustments of this product unless another person capable of rendering first aid and resuscitation is present.                                                                                                                                                                                                                                                                                                                                                          |

| Disconnect Power                         | To avoid electric shock, disconnect the main power by means of the power cord<br>or, if provided, the power switch.                                                                                                                                                                                                                                                                                                                                                                                        |

| Use Caution When<br>Servicing the CRT    | To avoid electric shock or injury, use extreme caution when handling the CRT.<br>Only qualified personnel familiar with CRT servicing procedures and precautions<br>should remove or install the CRT.                                                                                                                                                                                                                                                                                                      |

|                                          | CRTs retain hazardous voltages for long periods of time after power is turned off.<br>Before attempting any servicing, discharge the CRT by shorting the anode to<br>chassis ground. When discharging the CRT, connect the discharge path to ground<br>and then the anode. Rough handling may cause the CRT to implode. Do not nick<br>or scratch the glass or subject it to undue pressure when removing or installing it.<br>When handling the CRT, wear safety goggles and heavy gloves for protection. |

| Use Care When Servicing<br>With Power On | Dangerous voltages or currents may exist in this product. Disconnect power, remove battery (if applicable), and disconnect test leads before removing protective panels, soldering, or replacing components.                                                                                                                                                                                                                                                                                               |

|                                          | To avoid electric shock, do not touch exposed connections.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| X-Radiation                              | To avoid x-radiation exposure, do not modify or otherwise alter the high-voltage circuitry or the CRT enclosure. X-ray emissions generated within this product have been sufficiently shielded.                                                                                                                                                                                                                                                                                                            |

### Preface

This document describes the procedures required to certify the DAS 9200 Series and TLA 500 Series logic analyzers and their associated modules.

This document is intended for Tektronix service personnel only. It assumes that the reader is a trained technician, familiar with DAS 9200 Series and TLA 500 Series logic analyzers.

For additional information, refer to the following documents:

- The DAS Technician's Reference Manual 070-5959-XX

- The DAS Verification and Adjustment Procedures Manual 070-5961-XX

- The TLA 510/520 Service Manual 070-8976-XX

- The 92A96XX Service Manual 070-8247-XX

- The 92HS8 User Manual 070-5951-XX

- The DAS 9200 Systems/TLA 500 Systems Functional Verification Procedure DAS9200-AA

Preface

### Introduction

The purpose of these certification procedures is to enable the Tektronix Field Service organization to satisfy customer requests for traceable certification of the DAS 9200 and TLA 500 systems. (Often, the customer requires equipment certification to achieve or maintain ISO compliance.)

#### NOTE. These procedures are not intended for customer availability.

These procedures provide Tektronix Field Service Technicians with a standardized and documented procedure for traceable certification of DAS 9200 and TLA 500 Systems to national standards. After performing this procedure, the technician can generate and provide the customer with a Certificate of Traceable Calibration and, if required, a Certification Test Record. The technician can then apply appropriate calibration stickers to the mainframe and modules which make up the system. This provides the customer with documentation and confidence in the measurement accuracy of their system.

This procedure does not verify the system to published specifications. It should generally be used in conjunction with the DAS 9200/TLA 500 Functional Verification Procedure. These Certification Procedures certify the accuracy of the primary references or adjustments; the Functional Verification Procedure verifies the functionality of the mainframe, module, and probes. Although not required for traceable certification, if full verification of published specifications is specially requested by the customer, refer to the Performance Verification Procedures in the appropriate DAS 9200/TLA 500 Service Manuals.

This procedure is intended for use by Tektronix Field Service Technicians who have completed DAS9200 Service Training. Others with less training may need access to other reference documents, such as mainframe and module user manuals, for detailed information. (Refer to page xi for a partial list of related documents.)

Please check the Required Test Equipment table on page 6 to ensure you have the proper traceable test equipment, fixtures, tools, and materials, before beginning the procedures.

**CAUTION.** Check with the customer before disconnecting probes or cables from the system under test. It is desirable to use the customer's probes and cables when called for, but in some cases this may not be possible.

#### **Products Certified**

Table 1 lists the modules which can be certified, and the order in which they must be tested. Table 2 lists the modules which have no certifiable references.

These procedures support Tektronix-recommended product configurations only.

The recommended recertification interval for DAS 9200 and TLA 500 products is one year.

| Product |                                                            | Parameter                                                                                          | Comments                                                                                                                                                                         |

|---------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | DAS 9219/9220<br>Mainframe                                 | Time Base Accuracy:<br>100 MHz (Main)                                                              | Measured on Controller board                                                                                                                                                     |

| 2       | DAS 9221/TLA<br>5XX Mainframe                              | Time Base Accuracy:<br>100 MHz (Main)                                                              | Measured on Controller board                                                                                                                                                     |

| 3       | 92E9 Expansion<br>Mainframe                                | Time Delay Accuracy                                                                                | Measured on Expansion Slave board                                                                                                                                                |

| 4       | 92A16/92A16E<br>board                                      | Threshold Accuracy<br>Time Base Accuracy (92A16 only):<br>200 MHz Clock                            |                                                                                                                                                                                  |

| 5       | 92A96/C96<br>board                                         | Threshold Accuracy                                                                                 |                                                                                                                                                                                  |

| 6       | 92HS8 Master<br>Interface board<br>and Probe Cabi-<br>nets | Time Base Accuracy:<br>500 MHz Clock<br>200 MHz Clock<br>Threshold Accuracy<br>Calibrator Accuracy | Time base accuracy measured on<br>Memory board inside Probe<br>Cabinet.<br>Threshold Accuracy procedures<br>consist of checking one setting for<br>each DAC on one channel only. |

| 7       | 92S16/92SX109<br>board                                     | Pod Clock Outputs<br>Threshold Accuracy (External<br>Control Probe Input)                          | 92SX109 same as 92S16 without multiplexer.                                                                                                                                       |

| 8       | 92S32/92SX118<br>board                                     | Pod Clock Outputs                                                                                  | 92SX118 same as 92S32 without multiplexer.                                                                                                                                       |

#### **Table 1: Products Certified**

#### Table 2: Products Not Certified

| Product                  | Comments                                 |

|--------------------------|------------------------------------------|

| 92A60 Controller board   | No certifiable references or adjustments |

| 92A60 Memory board       | 1/                                       |

| 92A60D Memory board      | 1/                                       |

| 92A90 Controller board   | "                                        |

| 92A90 Memory board       | "                                        |

| 92A90D Memory board      | "                                        |

| 92A60/90 Buffer probe    | "                                        |

| 92HS8E Expansion board   | "                                        |

| Acquisition probes       | "                                        |

| Pattern Generator probes | "                                        |

| 92LAN board              | "                                        |

| 92LANSE board            | "                                        |

| 92C01/2/3 board          | "                                        |

### **Procedure Overview**

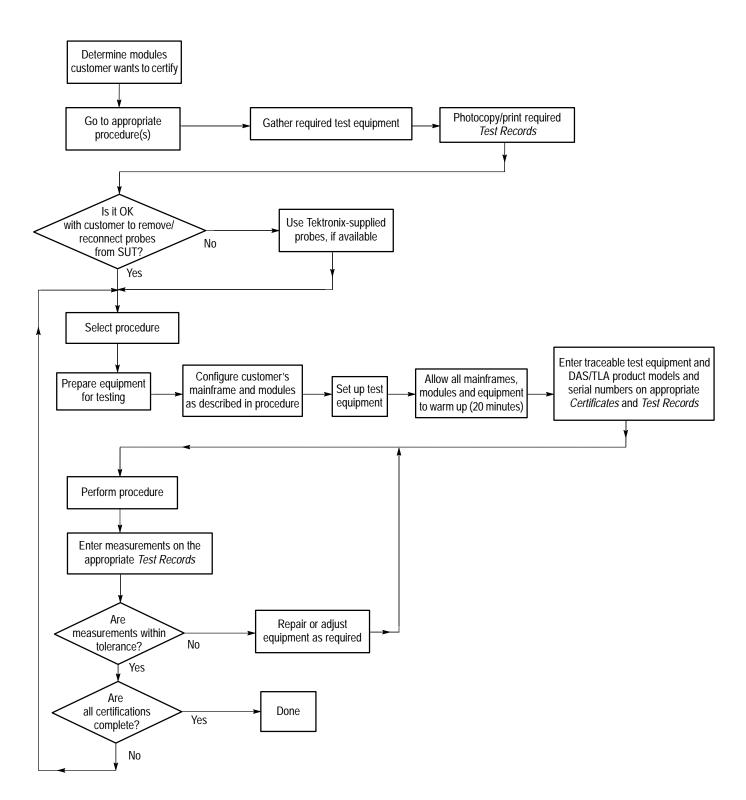

Figure 1 shows the general order of tasks that you will need to perform for certification.

Figure 1: Certification Procedure Tasks

### **General Information and Conventions**

The following general information and conventions apply throughout this section:

• Each test procedure begins with a table, similar to the one below, that provides information you need to know before starting the test.

| Equipment                                       | Universal Counter/Timer with Probe (item 1)         |

|-------------------------------------------------|-----------------------------------------------------|

| Required                                        | Dual Lead Adapter (item 7)                          |

|                                                 | Gold Square Pin (item 9)                            |

| Configuration Mainframe, configured as follows: |                                                     |

|                                                 | Top cover removed                                   |

|                                                 | Memory board removed; other boards may be installed |

| Prerequisites                                   | Warm-up time: 20 minutes, DAS and test equipment    |

|                                                 | Power-up diagnostics pass.                          |

|                                                 | No previous tests required.                         |

The item numbers after each piece of equipment refer to line numbers in Table 3, *Required Test Equipment*, which begins on page 6.

- The *Test Record* starts with header information that must always be filled out completely. The *Certificate Number* is the number of the actual *Certificate of Traceable Calibration* that you'll complete.

- Always fill out the *Incoming Data* entry on the *Test Record*. The *Outgoing Data* entry is required only if you perform a repair or adjustment to the module such that the certification tests must be performed again.

### **Equipment Required**

These procedures require the use of traceable signal sources and measurement instruments to ensure accuracy. Table 3 lists the equipment required for the procedures.

You can obtain an accuracy ratio of 4:1 or better by using the recommended equipment listed in the *Examples* column of Table 3. If your test equipment does not meet the minimum requirements listed in the table, your test results may be invalid.

#### Table 3: Required Test Equipment

| Ite | m Number and Description                           | Minimum Requirements                                                                                                 | Examples                                                                                                                                               | Where Used                                                                        |

|-----|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 1   | Universal Counter/Timer<br>with Probe <sup>1</sup> | 200 MHz frequency<br>measurement capability;<br>20 ppm time base accuracy<br>@25 MHz to 200 MHz;<br>10 Hz resolution | Tektronix DC 5010 Digital<br>Counter/Timer with P6125 5X Probe or<br>P6137 10X Probe <sup>1,2</sup> (with TM 5000<br>mainframe) or<br>Tektronix CMC251 | Procedure 1, 2, 4, 6                                                              |

| 2   | Oscilloscope with two<br>Probes <sup>1,3</sup>     | 350 MHz bandwidth;<br>2 ns/div;<br>delta time = 14.2 ns $\pm 0.9\%$<br>( $\pm 125$ ps)                               | Tektronix 2465B with P6137 probes or<br>Tektronix TDS 520A with P6139A<br>probes                                                                       | Procedure 3, 7, 8                                                                 |

| 3   | Digital Multimeter (DMM)                           | 4.5 digit; 0 V ± 0.5 mV;<br>±1.6 V ± 3 mV (0.19%)                                                                    | Tektronix DMM 252 <sup>4</sup> , DMM 254 <sup>4</sup> ,<br>DM2510, DM2510G or<br>Fluke 884X or 850X series                                             | Procedure 4, 5, 7                                                                 |

| 4   | DC Voltage Calibrator                              | 0 V $\pm$ 5 mV,<br>0 V $\pm$ 30 mV with <5 mV<br>adjustment resolution                                               | Fluke 34X series, Fluke 5100 series,<br>Fluke 5500A or<br>Wavetek 9100                                                                                 | Procedure 6                                                                       |

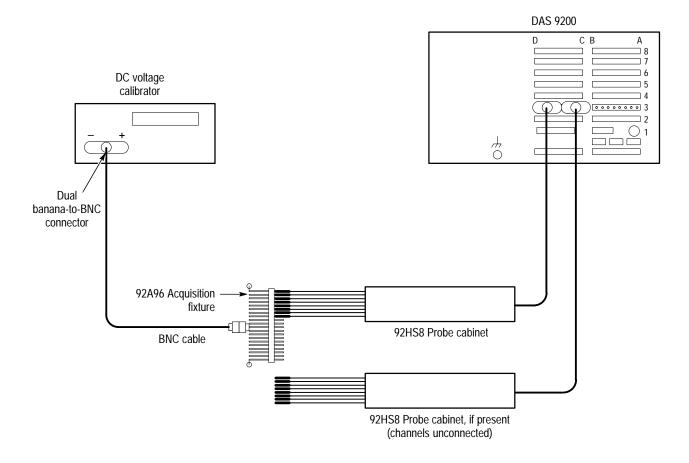

| 5   | 92A96 Acquisition Fixture                          | N/A                                                                                                                  | Refer to Appendix A on page 71 for parts list and build procedure.                                                                                     | Procedure 6                                                                       |

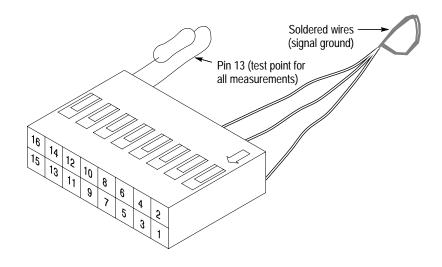

| 6   | Threshold Fixture                                  | N/A                                                                                                                  | Refer to Appendix B, on page 73 for parts list and build procedure.                                                                                    | Procedure 7                                                                       |

| 7   | Dual-Lead Adapter                                  | Two required                                                                                                         | Tektronix PN 015-0325-00                                                                                                                               | Procedure 1, 2, 3, 6, 7, 8                                                        |

| 8   | Subminiature-to-Miniature<br>Probe Adapter         | Two required                                                                                                         | Tektronix PN 013-0202-02                                                                                                                               | Procedure 3, 7, 8<br>Adapts the oscilloscope<br>probe to the dual-lead<br>adapter |

| 9   | Gold Square Pin                                    | Single gold square pin                                                                                               | Part of 131-1634-00, or equivalent                                                                                                                     | Procedure 2, 6                                                                    |

| 10  | Spring-Tip Ground<br>Connector                     | Spring-tip ground for probe                                                                                          | Tektronix PN 214-4125-00                                                                                                                               | Procedure 4                                                                       |

| 11  | DIP Clip                                           | 16 pin                                                                                                               |                                                                                                                                                        | Procedure 1                                                                       |

| 12  | DIP Clip                                           | 20 pin, narrow, modified for<br>two oscilloscope connec-<br>tions on pin 18 <sup>5</sup>                             |                                                                                                                                                        | Procedure 3                                                                       |

| 13  | BNC Cable                                          | 36 in; two required                                                                                                  | Tektronix PN 012-1341-00                                                                                                                               | Procedure 6                                                                       |

| 14  | Dual Banana-to-BNC<br>Connector                    | Two required                                                                                                         | Tektronix PN 103-0090-00                                                                                                                               | Procedure 6                                                                       |

#### Table 3: Required Test Equipment (Cont.)

| Item Number and Description Minimum Requirements |  | Examples                                                        | Where Used  |  |

|--------------------------------------------------|--|-----------------------------------------------------------------|-------------|--|

| 15 Ground Strap                                  |  | Tektronix PN 196-3353-XX (standard with the 92A96/92C96 Module) | Procedure 6 |  |

<sup>1</sup> Probes must be compensated. Refer to the oscilloscope or counter/timer manual for the correct probe compensation procedure.

- <sup>2</sup> The P6125 probe is a 5X probe. If you use a 10X probe, you must adjust threshold voltages accordingly.

- <sup>3</sup> For procedures requiring delta time measurements, you must compensate for oscilloscope channel-to-channel skew.

- <sup>4</sup> The handheld DMMs (DMM 252 and DMM 254) provide a 3:1 test accuracy ratio at ±1.6 V (4 V full-scale range).

- <sup>5</sup> Modify the DIP clip by soldering a second pin in parallel with pin 18.

### **Test Conditions**

The certification procedures must be performed in an environment that is within the instrument's normal electrical and environmental operating parameters, following a minimum 20-minute warm-up period.

These procedures support Tektronix-recommended product configurations only.

Introduction

## Procedure 1: DAS 9219/9220 Mainframes

This procedure verifies the accuracy of the 100 MHz Time Base Clock on the Controller board.

#### **Time Base Accuracy**

| Equipment     | Universal counter/timer with probe (item 1)                        |  |  |  |

|---------------|--------------------------------------------------------------------|--|--|--|

| Required      | Dual lead adapter (item 7)                                         |  |  |  |

|               | 16-pin DIP clip (item 11)                                          |  |  |  |

| Configuration | Mainframe, configured as follows:                                  |  |  |  |

|               | Top cover and card cage door removed                               |  |  |  |

|               | Memory board removed <sup>6</sup> ; all instrument modules removed |  |  |  |

| Prerequisites | All power-up diagnostics pass (before removing Memory board)       |  |  |  |

|               | Warm-up time: 20 minutes (test equipment and DAS/TLA mainframe)    |  |  |  |

|               | Counter/timer probe compensated                                    |  |  |  |

|               | No previous procedures required                                    |  |  |  |

<sup>6</sup> Before removing the Memory board, verify that the power-up diagnostics pass.

Test Equipment Setup

Set up the test equipment as follows:

| Counter/Timer with 5X Probe | Channel A:                       |

|-----------------------------|----------------------------------|

|                             | MODE FREQ A                      |

|                             | TERM 1 MΩ                        |

|                             | SLOPE +                          |

|                             | ATTN X1                          |

|                             | COUPL DC                         |

|                             | CH A LEVEL +0.740 V <sup>7</sup> |

|                             | AVGS –1                          |

<sup>7</sup> Value shown is for a 5X probe. For a 10X probe, value should be 0.372 V.

#### 100 MHz Time Base Clock Procedure

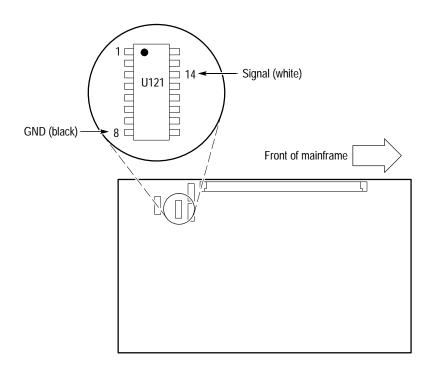

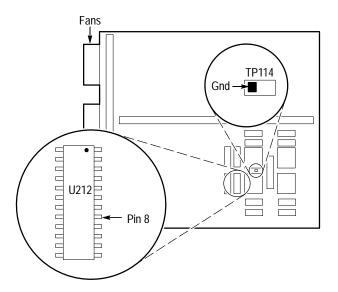

- **1.** Connect the counter/timer probe GND to U121 pin 8 on the Controller board. (See Figure 2.)

- **2.** Connect the counter/timer probe input to U121 pin 14 and record the measured frequency on the *Test Record*. Verify that the value is within the allowable range.

Figure 2: Controller Board 100 MHz Time Base Clock Test Point Locations (DAS 9219/9220 Mainframes)

# **Certification Test Record**

#### DAS 9219/9220 Mainframe

Instrument Model:

Serial Number:

Verification Performed by:

Certificate Number:

Verification Date:

### Time Base Accuracy Test Data

| Characteristic     | Specification   | Tolerance                  | Procedure<br>Reference | Incoming Data | Outgoing Data |

|--------------------|-----------------|----------------------------|------------------------|---------------|---------------|

| 100 MHz Main Clock | 100 MHz ± 0.01% | 99.99 MHz to<br>100.01 MHz | Page 10,<br>Step 2     |               |               |

## Procedure 2: DAS 9221 and TLA 510/TLA 520 Mainframes

This procedure verifies the accuracy of the 100 MHz Time Base Clock on the Controller board.

#### **Time Base Accuracy**

| Equipment<br>Required | Universal counter/timer with probe (item 1)<br>Dual lead adapter (item 7) |  |  |  |

|-----------------------|---------------------------------------------------------------------------|--|--|--|

|                       | Gold square pin (item 9)                                                  |  |  |  |

| Configuration         | Mainframe, configured as follows:                                         |  |  |  |

|                       | Top cover and card cage door removed                                      |  |  |  |

|                       | All instrument modules removed                                            |  |  |  |

| Prerequisites         | Warm-up time: 20 minutes (test equipment and DAS/TLA mainframe)           |  |  |  |

|                       | Counter/timer probe compensated                                           |  |  |  |

|                       | No previous procedures required                                           |  |  |  |

|                       | All power-up diagnostics pass                                             |  |  |  |

Test Equipment Setup

Set up the test equipment as follows:

| Counter/Timer with<br>5X Probe | Channel | A:     |                       |  |  |

|--------------------------------|---------|--------|-----------------------|--|--|

|                                | MODE    | FREQ A |                       |  |  |

|                                | TERM    | 1 MΩ   |                       |  |  |

|                                | SLOPE   | +      |                       |  |  |

|                                | ATTN    | X1     |                       |  |  |

|                                | COUPL   | DC     |                       |  |  |

|                                | CH A LE | VEL    | +0.740 V <sup>8</sup> |  |  |

|                                | AVGS    | -1     |                       |  |  |

<sup>8</sup> Value shown is for a 5X probe. For a 10X probe, value should be 0.372 V.

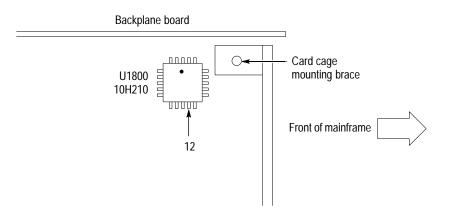

100 MHz Time Base Clock Procedure

- 1. Connect the counter/timer probe ground to TP4800 (GND).

- 2. Connect the counter/timer probe input to U1800 pin 12 and record the measured frequency on the *Test Record*. (See Figure 3.) Verify that the value is within the allowable range.

## **Certification Test Record**

### DAS 9221 and TLA 510/TLA 520 Mainframes

Instrument Model:

Serial Number: \_\_\_\_\_

Certificate Number:

Verification Performed by:

Verification Date:

### Time Base Accuracy Test Data

| Characteristic     | Specification   | Tolerance                  | Procedure<br>Reference | Incoming Data | Outgoing Data |

|--------------------|-----------------|----------------------------|------------------------|---------------|---------------|

| 100 MHz Main Clock | 100 MHz ± 0.01% | 99.99 MHz to<br>100.01 MHz | Page 14,<br>Step 2     |               |               |

## Procedure 3: 92E9 Expansion Mainframe

This procedure verifies that the 92E9 Expansion Mainframe is correctly synchronized with the master mainframe clock to ensure overall system timing accuracy.

#### **Time Delay Accuracy**

| Equipment                      | Oscilloscope with probes (item 2)                                                                                               |  |  |  |  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Required                       | Dual-lead adapters (2) (item 7)                                                                                                 |  |  |  |  |

|                                | Subminiature-to-miniature probe adapters (2) (item 8)                                                                           |  |  |  |  |

|                                | 20-pin DIP clip, narrow, modified for two oscilloscope connections on pin 18 (item 12)                                          |  |  |  |  |

| Configuration                  | Expansion Mainframe(s), configured as follows:                                                                                  |  |  |  |  |

|                                | Top cover and card cage door removed                                                                                            |  |  |  |  |

|                                | All instrument modules removed                                                                                                  |  |  |  |  |

| Prerequisites                  | Warm-up time: 20 minutes (test equipment, DAS master mainframe, and expansion mainframe(s))                                     |  |  |  |  |

|                                | Oscilloscope probes compensated <sup>9</sup>                                                                                    |  |  |  |  |

|                                | Power-up diagnostics pass                                                                                                       |  |  |  |  |

|                                | Must have passed either <i>Procedure 1: DAS 9219/9220 Mainframes</i> or <i>Procedure 2: DAS 9221 and TLA 510/520 Mainframes</i> |  |  |  |  |

| <sup>9</sup> The following pro | ocadura calls for a dalta tima maasurament. Bafora taking the                                                                   |  |  |  |  |

<sup>9</sup> The following procedure calls for a delta time measurement. Before taking the measurement, you must compensate for the oscilloscope channel-to-channel skew (in addition to the normal probe compensation).

#### Test Equipment Setup

Set up the test equipment as follows:

| Oscilloscope | A Trigger        |              |

|--------------|------------------|--------------|

|              | Source           | Ch 1         |

|              | Coupling         | AC           |

|              | Slope            | +            |

|              | Mode             | Auto         |

|              | Trigger Level    | Mid-position |

|              | A Time Base      | 5 ns/Div     |

|              | Ch 1 and Ch 2 Ve | ertical      |

|              | Coupling         | AC           |

|              | Impedance        | 1ΜΩ          |

|              | Bandwidth        | Full         |

|              | V/Div            | 500 mV/Div   |

#### Time Delay Procedure

The following procedure measures the delay between two different stages of the clock signal.

**CAUTION**. Use extreme caution when connecting the DIP clip to U265. Shorting pins to ground or to other pins will destroy the device. Make all connections with the mainframe power off.

- **1.** Power off the mainframes before connecting the DIP clip or any test equipment.

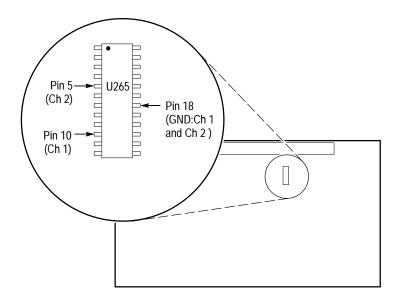

- **2.** Using the DIP clip, connect the Ch 1 scope probe input to U265 pin 10 on the Expansion Slave board. (See Figure 4.) Connect the ground lead to U265 pin 18.

- **3.** Connect the Ch 2 scope probe to U265 pin 5 and the ground lead to U265 pin 18.

Figure 4: DAS 92E9 Expansion Slave Board Test Point Locations

- **4.** Power on the master mainframe (which, in turn, powers on the expansion mainframe).

- 5. Adjust the scope trigger level for a stable waveform.

- **6.** Position the rising edge of the Ch 1 waveform at the left-most vertical graticule line and center the waveform vertically.

- 7. Center the Ch 2 waveform vertically.

- 8. Change the Horizontal Scale to 2 ns. Reposition the waveforms horizontally, if necessary, to locate the rising edge of Ch 1 at the left-most vertical graticule line.

- 9. Use the oscilloscope cursors to measure the time ( $\Delta$  delta time) from the 50% point of the rising edge of the Ch 1 waveform to the 50% point of the falling edge of the Ch 2 waveform. Record this value on the *Test Record*. Verify that the value is within the allowable range.

# **Certification Test Record**

### DAS 92E9 Expansion Mainframe

Instrument Model:

Serial Number: \_\_\_\_\_

Verification Performed by:

Certificate Number:

Verification Date:

### Time Delay Accuracy Test Data

| Characteristic | Specification        | Tolerance          | Procedure<br>Reference | Incoming Data | Outgoing Data |

|----------------|----------------------|--------------------|------------------------|---------------|---------------|

| Time Delay     | 14.2 ns $\pm$ 500 ps | 13.7 ns to 14.7 ns | Page 19,<br>Step 9     |               |               |

# Procedure 4: 92A16 Acquisition Board and 92A16E Expansion Board

This procedure verifies the accuracy of the 200 MHz Time Base Clock on the 92A16 board. This procedure also verifies the accuracy of the acquisition probe thresholds on the 92A16 and 92A16E boards.

#### **Time Base Accuracy**

This procedure checks the 92A16 200 MHz Time Base Clock.

| Equipment<br>Required | Universal counter/timer with probe (item 1)<br>Spring-tip ground connector (item 10)                                |  |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                       |                                                                                                                     |  |  |  |  |

| Configuration         | Mainframe, configured as follows:                                                                                   |  |  |  |  |

|                       | Top cover and card cage door removed                                                                                |  |  |  |  |

|                       | 92A16 installed in the lowest allowable slot number (slot 2 of DAS mainframe); all other instrument modules removed |  |  |  |  |

| Prerequisites         | Warm-up time: 20 minutes, DAS and test equipment                                                                    |  |  |  |  |

|                       | Counter/timer probe compensated                                                                                     |  |  |  |  |

|                       | Power-up diagnostics pass                                                                                           |  |  |  |  |

|                       | No previous tests required                                                                                          |  |  |  |  |

**Test Equipment Setup**

Set up the test equipment as follows:

| Counter/Timer with<br>5X Probe | Channel A: |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|--------------------------------|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                | MODE       | FREQ A | N Contraction of the second seco |  |

|                                | TERM       | 1 MΩ   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                | SLOPE      | +      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                | ATTN       | X1     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                | COUPL      | DC     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                | CH A LE    | VEL    | +0.740 V <sup>10</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                | AVGS       | -1     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

<sup>10</sup> Value shown is for a 5X probe. For a 10X probe, value should be 0.372 V.

200 MHz Time Base Clock Procedure

- **1.** Move to the 92A16 Trigger menu.

- 2. Press F1: START.

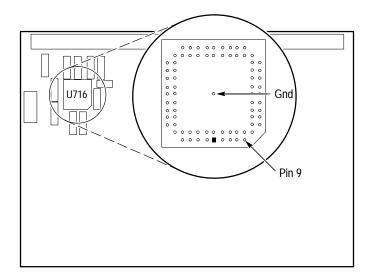

- **3.** Connect the counter/timer probe spring-tip ground to the Gnd test point (hole) on the back of the circuit board, near U716. (See Figure 5.)

- **4.** Connect the counter/timer probe input to U716, pin 9 and record the measured frequency on the *Test Record*. Verify that the value is within the allowable range.

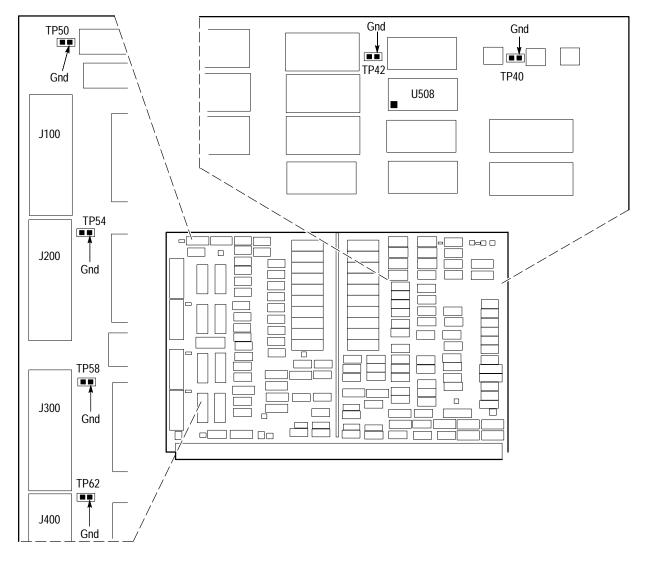

Figure 5: 92A16 Test Point Locations (back of board)

# **Threshold Accuracy**

This procedure verifies the threshold accuracy at the external control probe connectors (J400 and J600).

| Equipment                             | DMM (item 3)                                                                                                                                                    |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Required                              | Threshold fixture <sup>11</sup> (item 6)                                                                                                                        |

| Configuration                         | Mainframe, configured as follows:                                                                                                                               |

|                                       | Top cover and card cage door removed                                                                                                                            |

|                                       | 92A16 installed in the lowest allowable slot number (slot 2 of DAS mainframe); 92A16E modules installed in adjacent slots; all other instrument modules removed |

| Prerequisites                         | Warm-up time: 20 minutes (test equipment and DAS/TLA mainframe and modules)                                                                                     |

|                                       | All power-up diagnostics pass                                                                                                                                   |

| <sup>11</sup> For informatic page 73. | on about building the threshold fixture, refer to Appendix B, on                                                                                                |

Test Equipment Setup

Set up the test equipment as follows:

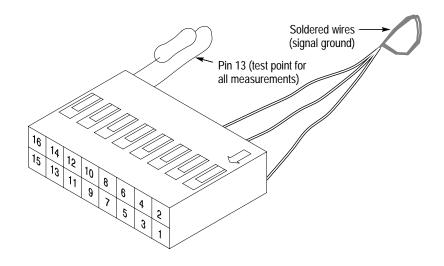

| Threshold Fixture | Connected to J400 (pod B connector) of the 92A16 module—pin 1 of threshold fixture connected to pin 1 of probe pod connector |

|-------------------|------------------------------------------------------------------------------------------------------------------------------|

| DMM               | Autorange                                                                                                                    |

|                   | Ground lead connected from DMM to pin 1 of threshold fixture (see following figure)                                          |

|                   | Positive lead connected to pin 13 of threshold fixture                                                                       |

#### Pod B/Pod C Threshold Procedure

- **1.** Make the following 92A16 Setup menu selections:

- Channel menu: Threshold Level→VAR→ 0.00V (Repeat this setting for each pod, including all 92A16E pods, if present)

- Trigger menu:

State One

If Word #1 = XX... (all don't cares)

- Then Begin Again

- 2. Press F1: START.

- **3.** Record the DMM voltage reading on the *Test Record*. Verify that the value is within the allowable range.

- 4. Move the threshold fixture to J600 (pod C connector).

**CAUTION.** When inserting the threshold fixture into a connector, be sure that the fixture is correctly oriented, pin 1-to-pin 1. Incorrect insertion can damage the instrument module.

5. Record the DMM voltage reading on the *Test Record*. Verify that the value is within the allowable range.

- 6. If any 92A16E modules are present, move the threshold fixture to the J400 and J600 connectors on those modules and record the DMM voltage reading for each connector on the *Test Record* for the 92A16E. (Each 92A16E module requires a separate *Test Record*.) Verify that the value is within the allowable range.

- 7. Press F1: STOP.

### DAS 92A16 Acquisition Board

| Instrument Model:          |                     |

|----------------------------|---------------------|

| Serial Number:             | Certificate Number: |

| Verification Performed by: | Verification Date:  |

### Time Base Accuracy Test Data

| Characteristic          | Specification  | Tolerance             | Procedure<br>Reference | Incoming Data | Outgoing Data |

|-------------------------|----------------|-----------------------|------------------------|---------------|---------------|

| 200 MHz Time Base Clock | 200 MHz ± 0.5% | 199 MHz to<br>201 MHz | Page 58,<br>Step 8     |               |               |

### Threshold Accuracy Test Data

| Characteristic  | Specification  | Tolerance               | Procedure<br>Reference | Incoming Data | Outgoing Data |

|-----------------|----------------|-------------------------|------------------------|---------------|---------------|

| Pod B Threshold | 0.000 V ± 8 mV | -0.008 V to<br>+0.008 V | Page 26,<br>Step 3     |               |               |

| Pod C Threshold | 0.000 V ± 8 mV | -0.008 V to<br>+0.008 V | Page 26,<br>Step 5     |               |               |

# DAS 92A16E Expansion Board

| Instrument Model:          |                     |

|----------------------------|---------------------|

| Serial Number:             | Certificate Number: |

| Verification Performed by: | Verification Date:  |

# **Threshold Accuracy Test Data**

| Characteristic  | Specification  | Tolerance               | Procedure<br>Reference | Incoming Data | Outgoing Data |

|-----------------|----------------|-------------------------|------------------------|---------------|---------------|

| Pod B Threshold | 0.000 V ± 8 mV | –0.008 V to<br>+0.008 V | Page 27,<br>Step 6     |               |               |

| Pod C Threshold | 0.000 V ± 8 mV | –0.008 V to<br>+0.008 V | Page 27,<br>Step 6     |               |               |

# Procedure 5: 92A96/92C96 Acquisition Board

This procedure verifies the accuracy of the 92A96/92C96 data and clock channel input thresholds.

| Equipment<br>Required | DMM (item 3)                                                                                                              |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------|

| Configuration         | Mainframe, configured as follows:                                                                                         |

|                       | Top cover and card cage door removed                                                                                      |

|                       | Mainframe lying on its right side, with power supply down                                                                 |

|                       | 92A96 or 92C96 installed in highest allowable slot (slot 7 for DAS, slot 3 for TLA), all other instrument modules removed |

| Prerequisites         | Warm-up time: 20 minutes (test equipment and DAS/TLA mainframe and modules)                                               |

|                       | No previous procedures required                                                                                           |

|                       | All power-up diagnostics pass                                                                                             |

#### **Threshold Accuracy**

This procedure verifies the accuracy of the data and clock channel input threshold levels.

**Test Equipment Setup** Set up the test equipment as follows:

|                 | DMM                     | Autorange                                                       |  |  |

|-----------------|-------------------------|-----------------------------------------------------------------|--|--|

| PRREF Procedure | <b>1.</b> Select the 92 | 2C96 Channel menu.                                              |  |  |

|                 |                         | EFINE THRESHOLD, and set both the Clock and Data to VAR –4.00V. |  |  |

|                 | <b>3.</b> Press F8: E2  | XIT & SAVE.                                                     |  |  |

|                 | 4. Select the 92        | 2C96 Clock menu.                                                |  |  |

|                 | 5. Select Exter         | rnal for the Module Clock selection.                            |  |  |

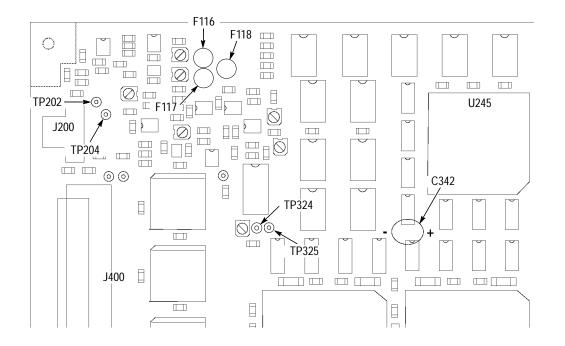

**6.** Refer to Figure 6 and connect the DMM's ground and positive input leads as follows:

Ground lead to +5 V (C342 +lead)

Positive input lead to PRREF (TP324)

7. Record the DMM voltage reading on the *Test Record*. Verify that the value is within the allowable range.

#### Figure 6: Data and Clock Threshold Test Point Locations

- **CREF/DREF Procedure** 8. Move the DMM's ground lead to TP325 (ground).

- **9.** Press F1: START, wait for the Slow Clock message to appear, and press F1: STOP.

- **10.** Move the DMM's positive input lead to CREF (TP202).

- **11.** Record the DMM voltage reading on the *Test Record* (the *CREF* –4.00 V *Threshold* entry). Verify that the value is within the allowable range.

- 12. Move the DMM's positive input lead to DREF (TP204).

- **13.** Record the DMM voltage reading on the *Test Record* (the *DREF* –4.00 V *Threshold* entry). Verify that the value is within the allowable range.

- 14. Select the 92C96 Channel menu.

- **15.** Press F5: DEFINE THRESHOLD, and set both the Clock and Data Thresholds to VAR +8.75 V.

- 16. Press F8: EXIT & SAVE.

- **17.** Press F1: START, wait for the Slow Clock message to appear, and press F1: STOP.

- **18.** Record the DMM voltage reading on the *Test Record* (the DREF + 8.75 V *Threshold* entry). Verify that the value is within the allowable range.

- **19.** Move the DMM's positive input lead to CREF (TP202).